# VLSI DESIGN OF ADVANCED-FEATURES AES CRYPTO PROCESSOR FOR DATA CRYPTOGRAPHY

## <sup>1</sup>Rashmi A, <sup>2</sup>Dr. Yogesh G S

<sup>1</sup>Student, <sup>2</sup>Professor, HOD East point college of engineering and technology

*Abstract-* AES is a mathematical justification of data concealment. It involves implementation on the very secure symmetric cryptography method using an FPGA (field-programmable gate array). This projected construction consists of an 8-bit stream of data and five primary components. We design two separate registration banks, Key-Register and State-Register, to hold the plain text, the keys, and intermediate data. To save space, shift-rows are added to the state register. We developed an 8-bit block that can transmit and receive 8-bit data and has four inner registers that are optimised for Mix-Columns. To make different Sub-Bytes better, we integrate and simplify them. To reduce power usage, we use clock gate technology into the architecture. For picture cryptography, this work proposes a 128-bit AES architecture.Verilog HDL is castoff create this design, and a Matlab & Modelsim 6.4 C tool are used to simulate it. The Synthesis Process tool from Xilinx measures performance.

#### Keywords- Advanced encryption system, Xilinx.

#### I. INTRODUCTION

Cryptography is a cipher or a system that is used to prevent anyone other then the intended recipient from receiving it. A message may be encoded using a cryptosystem. Only when the right algorithm and keys are used to decode the message can the receiver see the encrypted content. The main use of cryptography is the transmission of confidential information through computer networks. A clear-text document is transformed into crypto-text during the encryption process by applying a password and an algorithm of numbers to it. The block cypher AES algorithm of encryption uses multiple rounds of encryption with an encryption key. A block cypher is a kind of encryption that only encrypts a single piece of info at a time. The block size in standard AES encryption is 128 bits, about 16 bytes. The term "rounds" refers to the ten to fourteen times that the data is encrypted and decrypted throughout the encryption process, based on the size of the encryption key. On the Wikipedia article about AES encryption, this is described. AES is not a single piece of source code or software. Several applications have implemented AES encryption using source code encryption key.

One key is used by AES encryption throughout the encryption process. This distance might range from 128 bits (16 bytes) to 256 bits (32 bytes). The usage with a 128-bit key for encryption is mentioned to 128-bit encryption. With AES, same key is used for together encryption and decryption. A symmetrical encryption algorithm is what this is. Asymmetric encoding algorithms are individuals that use two distinct keys—a private and public key—in their operation. The binary code of data utilised in process of encryption serves as the encoding key. It is crucial to choose encoding keys are hard to guess since a single encoding key is utilised for both decoding and encrypting data.

#### II. RELATED WORK

This paper demonstrates the improved power and electromagnetic side-channel attack resistance for 128-bit Advanced Encryption Standard (AES) [1]. This paper presents an cimproved clocking methodology for a more efficient and reliable system[2]. As approved by the National Institute of Standards and Technology (NIST), the AES algorithm is capable of using cryptographic keys of 128, 192, and 256 bits to encrypt and decrypt data in blocks of 128 bits. It can be used by various departments and agencies for cryptography [3]. This survey provides an overview of advanced encryption system as a block cipher for high throughput applications which includes encryption and dataauthentication on FPGA system. [4]. This paper suggests the use of crptographic components for RFID tags whichare of low cost and consume less power [5]. This paper presents a low area, low power AES-CCM authenticated encryption IP core. The proposed AES-CCM core combines a low area 8-bit single S-box AES encryption core, improved iterative structure and other optimized circuits [7].

#### III. PROPOSED SYSTEM

The mask AES core and clock gate are castoff in the AES implementation to create the encryption masks. 128 bit encryption is performed using the maskedAES core. In instruction to conserve space compared to a fully unrolled implementation, the procedure is approved out in 10 cycles, calculating 1 round every cycle. The suggested masked AES is seen in the figure below. When a random mask is second-hand to first mask the unique data (plaintext). The "Nano AES core" is then fed the plaintext and the mask, which encrypts this data using the secret key. The module receives result masked cipher-text and outputs the desired cipher-text. 1) The Shift-Rows are contained into the State-Register in order to minimise the necessary logic.

2) We share the Sub-Bytes block with the key-expansion and encryption phases after optimising it.

3)Based on the assembly of the 8-bit datapath, which is tracked by Add-Round-Key, we develop an optimised 8-bit block for Mix-Columns with 8-bit input and output. As a consequence, Add-Round-Key receives the results byte by byte. cannot essential to save the outcomes in the register or make the datapath for the Key-Register 32 bits longer than this is for 32-bit Mix-columns.

4) The clock gating approach is used in many portions of the project to lesser the power consumption, which consequences in a lower power consumption.

We use the clock gating approach in several design elements to cut down on dynamic power usage. On State-Register, the internal register of Mix-Columns, Key-Register, and RCON, the clock gating is independently applied. The timer of State-Register and Mix-Columns is twisted off to save power meanwhile these two chunks are not utilised during the key expansion period, for example, which is when the greatest power is conserved.

#### **ENCRYPTION BLOCK DIAGRAM**

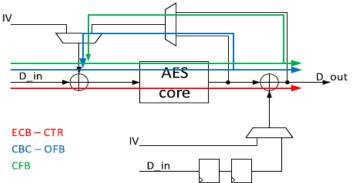

Encryption data flow: ECB, CBC, OFB, CFB, and CTR modalities with a single AES core design.

Fig1. Encryption block diagram

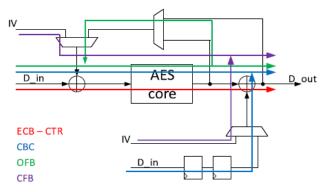

### **DECRYPTION BLOCK DIAGRAM**

### **IV. AES ALGORITHM**

Fig2. Decryption block diagram

AES never uses bits for computation; instead, it uses bytes. As a result, AES considers a plaintext block's 128 bits to be 16 bytes. For computation as a matrix, these 16 bytes are organised into 4columns and 4 rows.

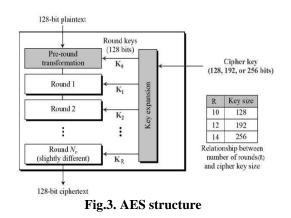

In difference to DES, the sum of cycles in AES varies and is grounded on the extent of the key. For 128-bit keys, AES employs 10 rounds; for 192-bit keys, 12 rounds; and for 256-bit keys, 14 rounds. A separate 128-bit round key, derived from the initial AES key, is used for respectively of these rounds.

The dimension of the key affects a variability of AES factors. For instance, if a key's size is 128 bits, then there are 10 rounds, but there are 12 and 14 rounds for keys of 192 and 256 bits, respectively. The 128 bit key is now the furthermost prevalent key size that will likely be employed. Consequently, this explanation of the procedure used by AES describes this specific implementation.

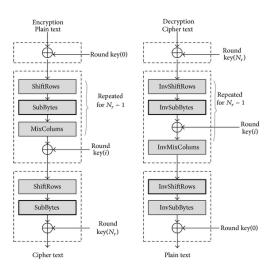

The Add rounds key stage is the first period of this algorithm, which is tracked by a total of nine rounds of four phases and a tenth rounds of three stages. This holds true for decryption as glowing as encryption, with an exception that the procedure used for decryption is the opposite of the encryption method at each point of a round. These are the 4 phases:

- 1. Replace bytes

- 2. Reverse rows

- 3. Mix Columns

- 4. Insert aRound Key

The Mix Column stage is simply skipped in the tenth round. The decryption algorithm's first nine rounds are as follows:

- 1. Rows with inverse shift

- 2. Bytes that act in reverse

- 3. Reverse Round Add Key

- 4. Columns with inverse mix

The method of AES decryption and encryption is exposed in the drawing below. An AES cypher text's decryption procedure resembles its encryption procedure in reverse. The four procedures are divided into rounds.

- Add round key

- Mix columns

- Shift rows

- SubstitutionByte

analyze the input data from the gesture sensor and classify different gestures based on predefined patterns or machine learning techniques.

The following graphic provides the AES structure's schematic.

The method of AES decryption and encryption is exposed in the drawing below. An AES cypher text's decryption procedure resembles its encryption procedure in reverse. The four procedures are divided into rounds.

- Add round key

- Mix columns

- Shift rows

- SubstitutionByte

Fig.4.AES encryption and decryption

### V. SOFTWARE DESCRIPTION

The simulation tool used here is Isim simulator which provides a total, full featured HDL stimulator integrated within ISE. With the tight integration of Isim within the design environment, HDL simulation can now be an even more essential phase within your design flow. The key features of Isim simulator are mixed language support, power analysis and optimization using SA IF, native support for all RIP blocks, memory editor for viewing and debugging memory elements, no special license requirement single click recompile and relaunch of simulation, integrated with IS design suite and plan ahead application multithread complete compilation, post processing capabilities, easy to use one click compilation and simulation.

The synthesis tool used is Xlinix ISE 14.7

The four fundamental steps in all digital logic design are:

1. Design – The circuit's description in a diagram or computer code.

2. Synthesis – the intermediary conversion of EDIF (FPGA code) format to human-readable circuit description. It entails validating the syntax and integrating all of these individual design files into one file.

3. Place&Route- where the circuits finalized layout is created. This is how the FPGA translates the EDIF into logic gates..

4. Program – Through the use of programming (.bit) files, the FPGA is updated to reflect the design.

The flow chart for gesture recognition is as shown below

## VI IMPLEMENTATION

The final recreation results for AES encryption and decryption shown in the snapshots given below, which includes snapsots at various stages of implementation.

Fig 5. Simulation results

Fig 5. Shows recreation result during substitution byte procedure

Fig 6.Simulation result

Fig 6. Shows the recreation result for shift rows procedure.

Fig 7. Shows the recreation result for add round key procedure.

Fig 8: Simulation result

The fig 8. shows the final recreation result for AES encryption and decryption in hexadecimal form.

Fig 9: Simulation result

The fig 9 provides the final recreation results for AES text encryption and decryption output

**RTL Schematic**

| AES_TOP_FINAL      |  |  |                 |  |  |  |  |  |

|--------------------|--|--|-----------------|--|--|--|--|--|

| key(127 <u>:0)</u> |  |  | dec_data(127:0) |  |  |  |  |  |

| text_in(127:0)     |  |  | enc_data(127:0) |  |  |  |  |  |

|                    |  |  |                 |  |  |  |  |  |

|                    |  |  | dec_complete    |  |  |  |  |  |

|                    |  |  | enc_complete    |  |  |  |  |  |

| rst                |  |  |                 |  |  |  |  |  |

| AES_TOP_FINAL      |  |  |                 |  |  |  |  |  |

### Fig 10: RTL schematic of AES block

Fig 10. provides the RTL schematic for AES block in which Clock signal and text\_in are considered as input and dec\_data as output. **VII RESULTS**

|                                                                    | Device Utilization Summary |           |             | E       |

|--------------------------------------------------------------------|----------------------------|-----------|-------------|---------|

| Slice Logic Utilization                                            | Used                       | Available | Utilization | Note(s) |

| Number of Slice Registers                                          | 1,066                      | 207,360   | 1%          |         |

| Number used as Flip Flops                                          | 1,066                      |           |             |         |

| Number of Slice LUTs                                               | 3,900                      | 207,360   | 1%          |         |

| Number used as logic                                               | 3,882                      | 207,360   | 1%          |         |

| Number using O6 output only                                        | 3,882                      |           |             |         |

| Number used as exclusive route-thru                                | 18                         |           |             |         |

| Number of route-thrus                                              | 18                         |           |             |         |

| Number using O6 output only                                        | 18                         |           |             |         |

| Number of occupied Slices                                          | 1,670                      | 51,840    | 3%          |         |

| Number of LUT Flip Flop pairs used                                 | 4,155                      |           |             |         |

| Number with an unused Flip Flop                                    | 3,089                      | 4,155     | 74%         |         |

| Number with an unused LUT                                          | 255                        | 4,155     | 6%          |         |

| Number of fully used LUT-FF pairs                                  | 811                        | 4,155     | 19%         |         |

| Number of unique control sets                                      | 144                        |           |             |         |

| Number of slice register sites lost<br>to control set restrictions | 418                        | 207,360   | 1%          |         |

| Number of bonded <u>IOBs</u>                                       | 518                        | 1,200     | 43%         |         |

| IOB Latches                                                        | 1                          |           |             |         |

| Number of BlockRAM/FIFO                                            | 3                          | 288       | 1%          |         |

#### Table 1. Device utilization summary

Table 1. indicates the device utilization summary using xilinx synthesis tool which illustrates its performance.

| Table 2. Comparison |         |       |       |       |         |          |  |  |  |

|---------------------|---------|-------|-------|-------|---------|----------|--|--|--|

| S.                  | Method  | Area  |       |       |         |          |  |  |  |

| No                  | Name    | Slice | Flip  | LUT   | Max     | Gate     |  |  |  |

|                     |         |       | Flops |       | Delay   | Delay    |  |  |  |

| 1                   | Normal  | 7734  | 21207 | 21207 | 160.860 | 25.302ns |  |  |  |

|                     | AES     |       |       |       | ns      |          |  |  |  |

|                     | Design  |       |       |       |         |          |  |  |  |

| 2                   | Propose | 1670  | 1066  | 3900  | 3.405ns | 2.923ns  |  |  |  |

|                     | d AES   |       |       |       |         |          |  |  |  |

|                     | design  |       |       |       |         |          |  |  |  |

Table 2. shows the comparison between the proposed AES design and normal AES design. **VII. CONCLUSION**

Inconclusion, AES is a highly secure symmetric encryption method that is extensively utilised in several applications and networks. AES is a good algorithm for small Internet of Things devices. The architectue comprised two designated register banks for storing simple text, keys, and results in intermediate stages, as well as an 8-bit data route. Shift-Rows were executed within the State-Register to minimise the necessary logic. Additionally, the architecture shared an optimised subblock of bytes with the encryption and key expansion phases. In addition, we created mix-Columns, a suitable block for low-area design, with 8-bit input and output. We used the clock gating approach in several design blocks to lower the size and power consumption, which resulted in a smaller footprint on the Virtex 5 xcVLX330T FF1738-2 board.